명령어 집합의 함수

모든 프로세서는 적어도 다음 작업을 수행할 수 있어야 합니다.

기본 기능

- 산술 연산 및 논리 연산

- 메모리와의 데이터 전송 : 프로세서와 메모리 사이에 데이터를 주고 받아야한다.

- 조건부 분기 (ex, if문)

- 상태를 확인할 수 있는 방법이 필요합니다.

- 조건이 충족되거나 충족되지 않을 경우 분기할 대상 메모리 주소 필요

그렇지 않으면 다음 지시.

- 점프 및 서브루틴 링크(절차 호출)

- 분기를 위해 광범위한 대상 메모리 주소 필요

- 프로시저 호출에 반송 주소가 필요합니다.

추가 기능: 예

- 레지스터 간, I/O 또는 공동 프로세서(co-processor)로 데이터 이동

co-processor : FPU, MMU

- 예외 및 인터럽트 지침 : 상태값 저장하고 명령어 수행하고 다시 돌아온다.

명령 집합 분류

추상 데이터 유형

- Object(개체) = 레지스터 및 메모리

- Operation(작동) = Instructions (설명, 지시)

- C 코드: a = b + c

- MIPS '코드': a, b, c 추가

* 피연산자 vs 레지스터

명령 집합 분류

- Machine : 레지스터 수/종류

0 (stack machine) 1(accumulator machine)

small (2-6) 일반 레지스터(예: 16, 32 이상)

- 명령당 주소 수

- 0 (stack machine)

- 1 (accumulator machine)

- 2 (일반 레지스터)

- 3 (일반 레지스터)

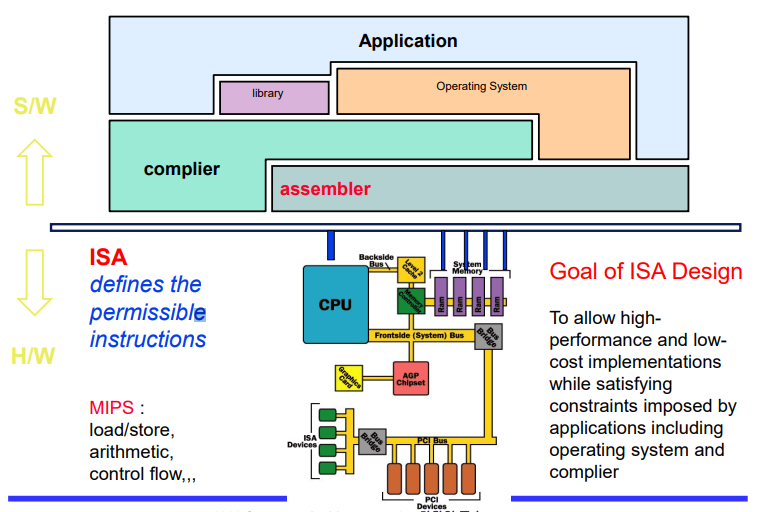

Instruction Set Architecture (ISA)

ISA : 허용되는 지침을 정의합니다.

MIPS : 불러오기/저장, 산술, 제어 흐름,...

ISA 설계 목표

운영 체제 및 컴파일러를 포함한 애플리케이션이 부과하는 제약 조건을 충족하면서 고성능 및 저비용 구현을 가능하게 함

ISA에 대한 간략한 역사적 관점

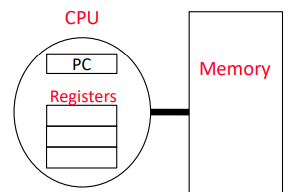

* ISA는 다음을 정의합니다.

- 시스템 상태(예: 레지스터, 메모리, 프로그램 카운터)

- CPU가 실행할 수 있는 명령

- 이러한 각 지침이 시스템 상태에 미치는 영향

* 범용 레지스터

- 레지스터는 어떤 용도로든 사용할 수 있습니다.

- 예: MIPS, ARM, x86

* Register - memory 구조

- 하나의 피연산자가 메모리에 있을 수 있다(예: accumulators(축전기)).

- 예: x86 프로세서, Motorola 68000

* Register-register 구조 (load-store라고 함)

- 모든 피연산자는 레지스터에 있어야 합니다.

- 메모리에 레지스터를 저장(store)하고 저장한 값을 다시 CPU로 불러올 수(load) 있다.

- 예: MIPS, ARM

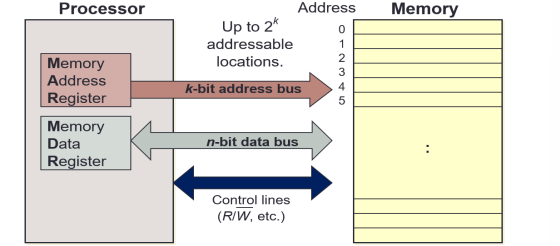

메모리 주소 지정 모드

메모리 주소 및 내용

- k-bit 주소를 지정하면 주소 공간이 2^k 크기입니다.

- 각 메모리 전송은 n비트의 한 단어로 구성됩니다

* 주소 지정 모드 (Addressing Mode)

: 어셈블리언어로 피연산자를 지정하는 방법

명령 형식: 길이, 작동

■ 가변 길이 지침

- 80x86: 1~17바이트(1: 짧은, 17: 길게), 디지털 VAX: 1~54바이트

- 다단계 가져오기 및 디코딩이 필요합니다.

- 보다 유연하고 복잡한 IS

■ 고정 길이 지침

- 대부분의 RISC(Reduced Instruction Set Computers)에 사용

- MIPS, 전원PC: 명령어의 길이는 4바이트입니다.

- 쉽게 가져오고 디코딩할 수 있습니다.

- 파이프라인 및 병렬화를 단순화합니다.

■ 하이브리드 명령 : 가변 길이 및 고정 길이의 혼합 명령

■ Opcode

- 원하는 작업을 지정하는 고유 코드, 각 동작마다 구별해주는 특별한 코드

■ 피연산자의 유형 및 크기

- 문자(8비트), 하프 워드(예: 16비트), 워드(예: 32비트),

단일 입력 부동 소수점(예: 단어 1개), 이중 입력

부동 소수점(예: 단어 2개).

명령 집합 인코딩

■ 결정해야 할 사항

- 레지스터 수

- 주소 지정 모드 수

- 명령의 피연산자 수

RISC vs CISC

■ Complex Instruction Set Computer(CISC, 복합 명령어 집합 컴퓨터) : x86-32 (IA32)

> 1000개의 명령, 각 1~15바이트

- 단일 명령으로 복잡한 작업 수행

- 10개의 주소 지정 모드

예: Mem [segment + reg + reg*scale + offset]

■ 데스크톱/서버

■ Reduced Instruction Set Computer(RISC, 축소 명령 집합 컴퓨터) : MIPS, ARM

- 지침 집합을 작고 단순하게 유지하여 보다 쉽게 하드웨어를 제작하고 작동한다

- ◦대략 200개의 명령, 각각 32비트, 3개의 형식

- 레지스터에는 항상 피연산자 존재

■ 에너지 효율성, 임베디드 시스템, 전화/태블릿

명령어 사용

■ 설계 및 실제 사용 작업 비교

간단한 명령어는 명령 빈도를 지배하며 CISC의 대부분의 명령어는 사용되지 않는다.

■ Amdahl의 법칙

다음 사각형의 지시사항은 자주 사용하므로 일반적인 사례를 빠르게 만들어서 성능을 향상시킨다.

* RISC-V: 자유롭고 개방적인 RISC 명령어 세트 아키텍처

요약

■ 동일한 ISA의 여러 가능한 구현

- x86 구현: 8086 (c. 1978), 80186, 286, 386, 486,

펜티엄, 펜티엄 프로, 펜티엄-4, 코어 i7, AMD 애슬론, AMD 옵테론, 트랜스메타 크루소, SoftPC

- MIPS 구현: R2000, R4000, R10000, ...

- JVM: 핫스팟, 피코자바, ARM 재젤...

- RISC-V: RV32I, RV32E, RV64I, RV128I 등

- 오픈 소스

■ ISA 클래스 : 스택, 어큐뮬레이터 및 범용 레지스터

■ 현재 대부분의 시스템은 범용 레지스터(GPR) 기반 ISA를 사용합니다.

'컴퓨터 구조' 카테고리의 다른 글

| Chapter5-2. 서로 다른 메모리 기술들 (0) | 2022.11.22 |

|---|---|

| Chapter.5-1 메모리 계층 이용 (0) | 2022.11.22 |

| Chapter.2-2 컴퓨터 언어 (0) | 2022.10.04 |

| Chapter.1 컴퓨터 추상화와 기술 (0) | 2022.10.03 |

| Chapter.0 과목소개 및 기술동향 (0) | 2022.10.03 |